HOME | SEARCH | REGISTER RSS | MY ACCOUNT | EMBED RSS | SUPER RSS | Contact Us |

http://top500.org/blog/category/feature-article/feeds/rss

04/27/18--03:14: UK Commits a

Billio...

05/01/18--01:43: \_Google Expands

<u>lts ...</u>

05/08/18--22:31: CERN Prepares

<u>for N...</u>

05/14/18--23:18: Did Google Al Just

....

05/21/18--00:41: \_Chip Startup

Unveil...

05/23/18--21:13: \_Intel Lays Out

<u>New ...</u>

05/29/18--23:13: \_NVIDIA Brings

<u>HPC a...</u>

06/06/18--01:51: <u>As Moore's Law</u>

Wind...

06/08/18--17:21: Summit Up and

Runni...

06/18/18--04:46: Sandia to Install

F...

06/23/18--03:55: Thomas Sterling

Tal...

06/24/18--17:37: US Regains

TOP500 C...

06/25/18--11:58: Distortions,

Trends...

06/25/18--21:43: CERN's Maria

Gi...

06/26/18--09:09: \_New GPU-

Accelerated...

06/29/18--06:39: Cloud Computing

<u>in ...</u>

07/02/18--09:23: \_Benchmarks in

<u>Hand,...</u>

07/05/18--13:27: \_European

Program to ...

07/16/18--09:18: \_A Tightening

Exasca...

07/20/18--10:16: \_AMD May Be

About to...

Deepmind is owned by Google, while Swiftkey is part of Microsoft. And even though Babylon is still operating independently, some of its investors are based in Sweden (Vostok New Ventures and KinnevikAB) and the US (NNC Holdings).

More to the point though, from a commercial perspective, the UK is not a major force in AI and is unlikely to be anytime soon. The biggest players are hyperscale companies based in the US (Google, Amazon, Microsoft, IBM, Facebook, and a few others) and China (Tencent, Baidu, and Alibaba). And that points to a larger challenge for the UK, namely, it has a relatively small population from which to draw the kind of data that drives most of the deep learning models that currently underlie AI. To develop a larger presence, it will have to establish at least one big multinational that can tap into foreign markets – a Barclays of AI, if you will.

Having said that, the overall rationale for a targeted investment in this area is well-justified, especially considering that the AI sector – something that barely existed five years ago – is projected to add more than £630 billion to Britain's economy by 2035. And given the R&D investments in artificial intelligence taking place in China, the US, Europe, Japan, and elsewhere, it behooves the UK to keep pace.

The growing importance of the AI sector also means government policies, and agencies implementing those policies, will have to be established to develop and manage this market. For example, the government plans to establish a new Office of Artificial Intelligence, as well as a Center for Data Ethics and Innovation. Working with those entities will be a new AI Council, an advisory group of business and academic leaders in the field. The government will also initiate public-private programs to attract AI talent, businesses, and investments to the UK.

Some of this investment is already happening organically. Google and Amazon have a substantial AI presence in the UK; Google has three offices in London

and another one planned for King's Cross, while Amazon has a total workforce of 24,000 in the country and plans to open two new robotics-enabled fulfilment centers in the near future. Meanwhile, Hewlett Packard Enterprise (HPE) recently partnered with ARM, and SUSE, and the universities of Bristol, Edinburgh and Leicester to deploy <u>three ARM-powered supercomputers</u> to be used for AI and big data work.

A number of international companies are also making AI-related investments in the country, either by partnering with UK organizations or by opening offices in the country. These include Elemental AI (Canadian AI research lab), Beyond Limits (American autonomous software developer), Ironfly Technologies (Hong Kong advanced financial analytics company), Astroscale (Japanese space debris removal tech company), Chrysalix (Canadian venture capital firm targeting AI and robotics), and Global Brain (Japanese venture capital firm with a focus on AI, blockchain, and robotics). In addition, <u>Bloomberg is</u> reporting that Microsoft, IBM and Facebook are "making undisclosed commitments, along with consulting firm PwC and pharmaceutical company Pfizer Inc."

On the academic side, the University of Cambridge Research Computing Service is making its latest £10 million supercomputer available to AI technology companies. This is almost certainly the <u>Wilkes2</u>, a 1.2-petaflop (Linpack) P100 GPU-accelerated cluster that is the UK's most powerful academic supercomputer. It's supported by a consultancy team at the university.

Can this strategy propel the UK into global AI dominance? Unlikely, given the current drivers of the AI market, the dominance of the US and China, and the size of the investment Britain can justify. But the country can certainly leverage its home-grown AI intellectual property and boost imports and exports of the technology. And that can form the basis of a vibrant industry that propels local businesses and increases productivity across all sectors of the economy.

#### 5/01/18--01:43: Google Expands Its GPU Cloud Options

Google has announced it is offering NVIDIA Tesla V100 GPUs for its HPC and machine learning cloud customers. But how will the company square this with its TPU cloud offering?

Google's deployment of the V100 follows that of Amazon, IBM, and Microsoft, who have offered this GPU in their respective clouds for some time. Amazon was the first provider to make it available to cloud customers, <u>when it rolled out</u> <u>its V100 instances in October 2017</u>. The V100 is currently NVIDIA's most advanced accelerator, offering 7.5 teraflops of double precision performance for HPC and 125 teraflops of tensor mixed precision performance for machine learning.

According to a <u>blog</u> posted on Monday by NVIDIA product managers Chris Kleban and Ari Liberman, the V100 solution will initially be offered in beta.

Customers will be able put up to eight of the GPUs, along with 96 vCPUs and 624 GB of memory in a single virtual machine. With that configuration, a user can tap into 60 teraflops of double precision or one petaflop of tensor performance. Kleban and Liberman write that HPC and deep learning workloads will realize a 40 percent performance boost with these latest GPUs.

In conjunction with the V100 launch, Google is also moving its Tesla P100 GPU cloud offering from beta to general availability. This one has almost the same configuration as the V100 offering, with up to 96 vCPUs and 624 GB of high bandwidth memory, but with a maximum GPU count of four. Given the lower relative performance of the P100 – 5.3 teraflops for HPC and 21.2 teraflops for machine learning – the P100 is a good deal less powerful than its younger sibling. The older K80 GPU, which Google has offered for some time and continues to support, is even less powerful than the P100. The company has priced them all accordingly, as can be seen from the table below.

| Google Cloud GPU Type |            |                                       | VM Configuration Options        |        |                   |

|-----------------------|------------|---------------------------------------|---------------------------------|--------|-------------------|

| NVIDIA<br>GPU         | GPU<br>Mem | GPU Hourly<br>Price**                 | GPUs                            | vCPUs* | System<br>Memory* |

| V100                  | 16gb       | \$2.48 Standard<br>\$1.24 Preemptible | <b>1,8</b> (2,4) coming in beta | 1-96   | 1-624 gb          |

| P100                  | 16gb       | \$1.46 Standard<br>\$0.73 Preemptible | 1,2,4                           | 1-96   | <b>1-624</b> GB   |

| K80                   | 12gb       | \$0.45 Standard<br>\$0.22 Preemptible | 1,2,4,8                         | 1-64   | 1-416 gb          |

Source: NVIDIA

Currently, the V100s will be available to Google customers in its Western and Central US regions, as well as parts of Western Europe. The P100 has a wider distribution and is available in Google's Western, Central and Eastern US regions, Eastern Asia, and Western Europe. The price table above applies only to US regions.

Google is ostensibly aiming the V100 and P100 at HPC and machine learning customers. In the blog announcement, two customers are mentioned: LeadStage, which is using both the V100 and P100 for optical character recognition on handwritten documents, and Chaos Group, which is employing the V100s for V-Ray Cloud rendering.

As we've reported before previously, Google has a divergent strategy with regard to machine learning in the cloud. Back in February, the company launched its Tensor Processing Units (TPUs) into its public cloud. The TPUs were custom-designed specifically for machine learning workloads and up until February had only been used internally by Google for its own applications like web search and language translation. By offering the TPUs to the general public, the web giant seemed to be probing customer interest in an alternative machine learning platform.

Google is renting its TPU board at a price of \$6.50 per hour. For that you get 180 machine learning teraflops and a minimal software stack based on the TensorFlow framework. Now for \$2.48 per hour, you can get a V100, which delivers 125 teraflops and comes with a much more extensive ecosystem of libraries and tools. It should be noted that the TPU boards, which contains four TPU chips, comes with 64 GB of high bandwidth memory (16 GB per chip), versus 16 GB on a single V100 device.

Given all that, the V100 would seem to be the better deal. However, a few months ago Elmar Haußmann, cofounder and CTO of RiseML, <u>compared the</u> <u>performance of four V100s in AWS against Google's four-TPU cloud board</u>, running an image classification training application (ResNet-50 on ImageNet). The idea was to match up both processor count and memory capacity. He found that the application performance for the TPU board and four-V100 setup was very similar, with the V100 only showing an advantage with smaller batch sizes. Moreover, Haußmann found that the TPU's performance per dollar was significantly better than the V100 based on the AWS pricing. Since Google's standard rate for its V100 for only about a third of the cost of its TPU board, Google's custom silicon would still come out on top in price-performance – at least for this particular application. That said, the preemptible pricing for the V100 is only about 20 percent that of the TPU, which would give the NVIDIA hardware the price edge.

For other machine learning applications, or perhaps even for ResNet 50 if a different software stack was employed, the V100 might be able to demonstrate a much clearer advantage. That would have to be determined on a case-by-case basis. Of course, if a customer is already invested in CUDA and NVIDIA machine learning libraries, the choice is pretty obvious. And certainly, for more conventional HPC applications, the V100 or any of the other GPUs would be the way to go, given the unsuitability of the TPU for non-machine learning software.

For the time being, Google is likely resigned to the fact that only its most adventurous customers will opt for the TPU platform. In the longer term though, the web giant would probably like to see this solution become a more standard option for its cloud customers, which would spread the cost of its chip design, production, and software support across a larger user base. In the meantime, Google seems willing to offer a somewhat confusing choice to its customers.

0 💼

05/08/18--22:31: <u>CERN Prepares</u> for New Computing Challenges with Large Hadron Collider Thanks to the discovery of the Higgs boson in 2012, CERN's Large Hadron Collider (LHC) has probably become the most widely recognized science project on the planet. Now almost 10 years old, the 27-kilometer ring of superconducting magnets is the world's largest and most capable particle accelerator. As such, it enables physicists to push the envelope of particle physics research.

Less well-known is the computing infrastructure that supports this effort – that of the The Worldwide LHC Computing Grid (WLCG), a network of more than 170 computing centers spread across 42 countries. Because LHC experiments can involve processing petabytes of data at a time, the computational, networking, and storage challenges for the project are immense. And when the next-generation High-Luminosity LHC (HL-LHC) is launched in 2026, these challenges will become even more formidable.

To find out more about what this entails, we asked Dr. Maria Girone, CERN's **openlab** CTO, to describe the high performance computing technology that undergirds the LHC work and talk about what kinds of hardware and software are being considered to support the future HL-LHC machine. Below is a lightly edited transcript of our conversation.

TOP500 News: Can you outline a typical computing workflow for an LHC application – for example, the workflow that resulted in the discovery of the Higgs boson particle?

**Maria Girone:** Workflows in high-energy physics typically involve a range of both data-intensive and compute-intensive activities. The collision data from the cathedral-sized detectors on the Large Hadron Collider needs to be filtered to select a few thousand interesting collisions from as many as one billion that may take place each second. The search for new phenomena is like looking for needles in enormous haystacks.

Once interesting collision events have been selected the processing-intensive period begins. The particles from each collision in the detectors are carefully tracked, the physics objects are identified, and the energy of all the elements are measured with extreme precision.

At the same time, simulation takes place on the Worldwide LHC Computing Grid, the largest collection of computing resources ever assembled for a single scientific endeavor. The WLCG produces a massive sample of billions of simulated beam crossings, trying to predict the response of the detector and compare it to known physics processes and potential new physics signals. In this analysis phase, the data from the detector is examined against predictions based on known background-only signals. When the data diverges statistically significantly from the background-only signals, we declare a discovery.

### TOP500 News: Do any of the experiments in the LHC project currently use deep learning of some other form of AI?

**Girone:** Neural networks and machine-learning techniques have been used in high-energy physics for many years. Optimization techniques, such as boosted decision trees, have been widely used in analysis. The field is now looking to expand the use of deep-learning and AI techniques based on the progress made by industry in these areas.

There is potential for applications throughout the data-selection and processing chain, which could increase the efficiency and performance of the physics searches. Other areas we are exploring include object identification based on 3D image-recognition techniques, improved simulation using adversarial networks, better monitoring via anomaly-detection techniques, and optimized resource use through machine-learning algorithms.

### TOP500 News: How are the computing challenges for the Large Hadron Collider different from typical HPC simulations?

**Girone:** The computing challenges of the LHC differ from typical HPC applications in the structure of the problem, the time-scale of the program and the number of contributors to the code. Whether processing a data event or producing simulations, each collision event can be treated independently. This means that the application lends itself to simple parallelization across many nodes.

With the LHC program running over multiple decades, there is need for software to be continuously improved. Occasionally, big components are reworked entirely, and there is also a lot of legacy code and services to support.

For many applications used in high-energy physics application, it is the case that several hundred people may well have contributed to the code base over many years. Traditional HPC simulations are often developed by much smaller groups of contributors, with more specific expertise in this area. Our use of

code developed by very large numbers of contributors makes it challenging to reach the level of optimization often achieved with other HPC codes.

TOP500 News: Given that the computing grid is spread around the world, what types of challenges are encountered with regard to sharing the large datasets associated with LHC work?

**Girone:** Data management has been a consistent area of development in LHC computing. We move petabytes per day and all the data needs to be monitored for consistency. We have become leaders in moving data using global networks. In the last few years, we have augmented the traditional techniques for moving and replicating data to provide real-time remote access to data files across the globe. Our global data-access model has helped to optimize the use of processing and storage resources, as well as making it possible to use commercial cloud and HPC resources in an opportunistic manner.

## TOP500 News: Can you describe what the High-Luminosity LHC will be able to do that cannot currently be done with the present-day LHC?

With the HL-LHC, about five to ten times more beam crossings will take place compared to today. Each of these crossings will result in about five times as many individual proton-proton collisions. This increase will help us to search for rarer signals and more precisely measure rare phenomena.

TOP500 News: As you look ahead to the High Luminosity LHC, what emerging technologies in hardware and software do you think are the most promising?

**Girone:** Looking forward to the HL-LHC, there are many interesting new technologies. The continued improvements in networking technologies will help us to continue distributing data efficiently. The progress made with various types of accelerators is being explored too. We have programs with GPUs and FPGAs that have the potential to dramatically improve the performance of the computing systems.

For software, better optimization and code modernization also hold great promise. Finally, new techniques like advanced data analytics and deep learning have the potential to change how analysis and reconstruction are performed, thus enabling us to process more data more efficiently.

Dr. Girone will present greater depth on the subject of computing challenges at CERN during the opening keynote of the <u>2018 ISC High</u> <u>Performance Conference</u>, which will take place on June 24-28 in Frankfurt, Germany. Her keynote address will take place on Monday, June 25.

Images: Maria Girone; CERN IT center. © CERN

#### 05/14/18--23:18: Did Google AI Just Pass the Turing Test?

Google has demonstrated an artificial intelligence technology that represents the most sophisticated example to date of a computer engaging in natural conversation with a human. Upon hearing the interaction, some listeners felt the software had convincingly passed the Turing test.

Even though it was developed in 1950, the <u>Turing test</u> is perhaps the most well-recognized way of measuring an AI system's capacity to demonstrate human intelligence. Developed by legendary computer scientist Alan Turing, the idea was to have a computer program converse with someone at a level where the person would be unable to tell if they were talking to a computer or a human. The test actually encompasses a good deal more complexity than that, but the gist of it is to prove whether or not a computer can pass as human.

Before we get too far into this, you need to watch the five-minute demonstration of the technology, known as Google Duplex, presented by Google CEO Sundar Pichai at last week's Google I/O 2018 event. The demo represents two phone conversations with different people in which Duplex successfully navigated some challenging exchanges. It's kind of mind-blowing, to the point you almost forget one of the participants is a computer.

As Pichai noted, the key to the technology is its ability to "understand to nuances of conversation." However, Duplex can't converse about everything. In a <u>blog</u> posted by Google Duplex lead Yaniv Yaniv Leviathan, Google Duplex lead, and Matan Kalman, engineering manager on the project,, being able to pull this off necessitated constraining the models to particular "closed domains" in order to develop the extensive conversational networks required for specific tasks. At this point, the technology is not sophisticated enough to produce a general-purpose AI conversationalist. In that sense, it might fail the Turing test once the conversation strayed into unsupported subject areas.

But the demonstration does illustrate how sophisticated those models are for the selected domains. Not only was Duplex able to converse naturally with the people on the phone, it was able to react appropriately when problems were presented – especially in the second phone call, when the person led the conversation astray. Leviathan and Kalman say the technology is also able to extract the meaning from context when ambiguities are presented. For example, the phrase "OK for four" could refer to 4 people or 4:00, depending on the conversation that preceded it.

The other thing that is immediately apparent is how well the technology has advanced for basic speech input and output. On the input side, the poor quality of the call on the first exchange and strong accent on the second exchange did not appear to trouble the Google software a bit. As far as Duplex's own voices, they appears to be based on the company's <u>WaveNet</u> <u>technology</u>, which has advanced speech generation to the point where it is all but indistinguishable from a real person. The addition of filler words like 'umm' and 'uh' and colloquialisms like "mmm-hmm" and "gotcha" is also a nice touch, adding some extra authenticity.

In the blog write-up, Leviathan and Matias offer a few details on the underlying technology, which they encapsulate thusly:

"At the core of Duplex is a recurrent neural network (RNN) designed to cope with these challenges, built using TensorFlow Extended (TFX). To obtain its high precision, we trained Duplex's RNN on a corpus of anonymized phone conversation data. The network uses the output of Google's automatic speech recognition (ASR) technology, as well as features from the audio, the history of the conversation, the parameters of the conversation (e.g. the desired service for an appointment, or the current time of day) and more. We trained our understanding model separately for each task, but leveraged the shared corpus across tasks. Finally, we used hyperparameter optimization from TFX to further improve the model."

No word on what hardware was used or how long the training took for any particular domain. According to Pichai, Duplex has been in the works for years, so presumably was developed over two or three generations of Tensor Processing Units (TPUs) and possible other hardware. As we reported last week, Google used this same I/O event to <u>unveil its third generation TPU</u>, which will be used to develop bigger and better neural networks for the web giant's internal needs. Special mention was made of using TPU 3.0 to improve the AI behind Google Assistant, which also happens to be the initial platform for Duplex.

In this case, the idea is to be able to tell Google Assistant to schedule something on your behalf by phone – a haircut appointment or restaurant reservation in the examples above. The app then does this phone magic offline via Duplex and notifies you when it completes the task. Ironically, this initial application is most useful for interacting with low-tech businesses that have yet to embrace modern online tools for managing appointments and reservations. But the underlying technology seems destined to expand into more lucrative areas like automated technical support, human intelligence gathering, or essentially any type of expert system that relies on personal interaction.

Google plans to start testing Duplex in Google Assistant this summer.

#### D5/21/18--00:41: <u>Chip Startup</u> <u>Unveils Processor That Aims to Scale</u> the Datacenter Power Wall

Tachyum, a Silicon Valley startup has unveiled a new processor that the company says can tackle a broad range of workloads in HPC, data analytics, artificial intelligence, and web services, while using a fraction of the power of existing chips.

0

In fact, the company claims that the new chip, known as "Prodigy," can deliver ten times the performance per watt of conventional processors across these application domains. And supposedly it will be able to do so in as little as 1 percent of the datacenter space. As a result, Tachyum predicts Prodigy will be

reduce datacenter costs by a factor of four.

The performance-per-watt story is a bit subtler than that, however. What the company is actually promising is computational power and efficiency on par with that of GPUs, but with a programming model that more closely resembles that of a CPU. Tachyum overall pitch is that Prodigy is a universal processor that can handle compute-intensive task like those found in HPC and machine learning, as well as more mainstream datacenter workloads, such as web services and analytics. And it can do so more efficiently than any of its competition.

According to Tachyum co-founder and CEO Radoslav 'Rado' Danilak, the energy efficiency of the chip and the financial benefits that accrue from is key to Prodigy's value proposition. The example he uses to illustrate the importance of this efficiency is Google. "They spent more than 10 billion dollars last year on the datacenter," he said recently. "With our technology they can easily save 6 billion, potentially 7 billion dollars, every year."

All of this is being accomplished without customized circuitry for specific applications. "Rather than build separate infrastructures for AI, HPC and conventional compute, the Prodigy chip will deliver all within one unified simplified environment, so for example AI or HPC algorithms can run while a machine is otherwise idle or underutilized," said Danilak. "Instead of supercomputers with a price tag in the hundreds of millions, Tachyum will make it possible to empower hyperscale datacenters to produce more work in a radically more efficient and powerful format, at a lower cost."

Even though the company is aiming Prodigy at a broad swathe of datacenter applications, it seems to be particularly focused on the burgeoning AI space, claiming that the processor's general-purpose nature will give it an advantage in tackling the various computational models being used in that domain. Tachyum is also pitching the chip as "an ideal tool" for the Human Brain Project. That effort is expected to require something on the order of 10 exaflops in order to support a real-time simulation of human brain. The company estimates it will take about 256 thousand of its processors to

accomplish this feat. The implication is that such a machine can be built by 2020.

According to Danilak, Prodigy's power efficiency and computational density will also make it suitable for powering containerized datacenters. The advantage here is that these containers can be located in the midst of large population centers, such that latency-sensitive applications like virtual reality-based gaming could be practical. Danilak also thinks that the chip could be employed in edge computing environment, like for example, cell phone towers, where they could be used by telcos to deliver novel types of media services.

Not a whole lot has been revealed about the specifics of Prodigy's design. In presentations, Danilak has outlined the architecture in general terms, noting that it will support some number of 100 Gbps Gigabit Ethernet and PCIe ports, as well as the capability for flash storage processing. From an instruction perspective it will have data path for things like AI and a universal control path for more general computation. That suggests they have found some way to combine the data parallelism of a GPU with the scalar model of a conventional CPU.

But the real critical piece of technology appears to be related to a solution of the "the wire problem" – the divergence between transistor speeds and the wires that feed them. As transistors get smaller the wires connecting them must get smaller as well, which slows down their transmission speed, hindering overall performance. The company has apparently attacked this problem at a fundamental level by changing the wire model. In a <u>video</u> recorded last year, Danilak says they have devised an architecture where the wires become "incredibly short," which gets around the problem by making wire speed "almost irrelevant."

At this point, Tachyum's business strategy is unknown. Even though the chip is now officially unveiled, the company has yet to announce system partners or early customer trials. The release date for Prodigy is also still up in the air. That said, if even half of these claims prove to be true, Tachyum could easily get acquired before the first chip leaves the fab. There is certainly no shortage of computer companies that would be interested in such technology.

#### **D** 05/23/18--21:13: <u>Intel Lays Out</u> <u>New Roadmap for AI Portfolio</u>

At Intel's inaugural AI DevCon conference this week, AI Products Group chief Naveen Rao updated their roadmap for its artificial intelligence chips. The changes will impact the much-anticipated Neural Network Processor, and to a lesser degree, its general-purpose products like Xeons and FPGAs.

News | TOP500 Supercomputer Sites

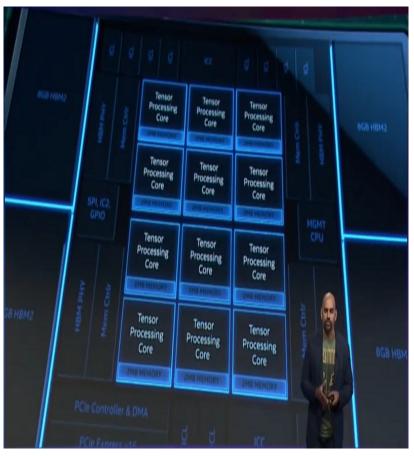

Naveen Rao presenting Lake Crest processor at AI DevCon. Source: video screen capture

During the conference's opening keynote, Rao began by noting that most machine learning currently runs on Xeon processors, and does so with respectable performance. "You may have heard that GPUs are 100x faster than CPUs," he told his developer audience. That's simply false."

The wide use of Xeon processors for these applications stems from the fact that the largest volume of machine learning computation, by far, is on the inferencing side, not the training side. Training is done once to build a model, while inferencing is performed innumerable times to query it. General-purpose CPUs like Xeon processors do inferencing reasonably effectively since it tends to be less computationally demanding than training and is more concerned with delivering a response in a reasonable of time to users.

To make those Xeon processors even more attractive for this work, Intel has added instructions in the latest Skylake processors that speed up neural network processing. In addition, the company has added software support and optimizations for these types of workloads, which have also increased performance. That work is ongoing.

Facebook's head of AI infrastructure, Kim Hazelwood, was brought out on stage to bolster that argument. She told the audience that the company currently runs a large segment of its inferencing work in areas like speech recognition, language translation and news ranking using regular CPU-powered servers. The main reason for this is that Facebook has a lot of

different types of applications to support and using general-purpose hardware for all of them across its vast datacenter empire is just easier-- and presumably less expensive. "Flexibility is really essential in this type of environment," said Hazelwood. What was left unsaid is that Facebook uses NVIDIA GPUs to do much of their offline AI training work.

In some cases though, CPUs are more attractive for training since the datasets are so large that the more limited local memory available on a GPU accelerator becomes too limiting. Right now, the largest local memory configuration for an NVIDIA V100 GPU is 32 GB.

Apparently, this was the critical factor for Novartis, which is using use Xeon Skylake gear to train image recognition models being used for drug screening. The images in question were so large and numerous that the model used 64 GB of memory – a third of the server's memory capacity – for this particular application. Moving from a single node to an eight-node cluster, Novartis was able to reduce training times from 11 hours to 31 minutes.

Having said all that, Rao said they are primarily positioning the Xeon platform for environments that mix training with other workloads or for dedicated setups for large-scale inferencing. The latter use case appears to overlap Intel's positioning of its FPGA products, but at this point Intel certainly realizes that most inferencing deployments are going to be CPU-based. Microsoft is the notable exception here, having already deployed Intel FPGAS at cloud scale on its Azure infrastructure for Al inferencing and a handful of other workloads.

Here, it's worth noting that Rao never brought up Knights Mill, <u>the Xeon Phi</u> <u>variant built for machine learning</u>. Three SKUs of the product were quitely launched in the fourth quarter of 2017 and are still listed on Intel's website, but their ommision here suggests Intel has given up on using Xeon Phi as a vehicle for this market, and, as we've suggested before <u>has likely has given up</u> <u>on Xeon Phi altogether</u>.

Which brings us to Lake Crest, Intel's first-generation Neural Network Processor (NNP) custom-built for training neural networks. Based on technology Intel acquired in the 2016 <u>Nervana acquisition</u>, Lake Crest was <u>supposed to debut last year</u>, but for whatever reason, is only now seeing the light of day. The chip is equipped with 12 cores, each of which have two deep learning math units. The device also contains 24 MB of local memory – 2 MB per core – backed by 32 GB of on-package high bandwidth memory (HBM2).

Lake Crest devices can be connected via an I/O link that delivers up to 2.4 terabits/second at less than 790 nanoseconds of latency. This high-speed communication link fulfills one of Intel's primary goals for this platform, namely that a high level of parallelism can be supported using multiple NNP processors.

The other principle design goal for the NNP platform is to provide high utilization of the available computational power. According to Rao, Lake Crest will deliver approximately 40 peak teraflops of deep learning performance, which is a good deal less than the 125 teraflops of its principle rival, NVIDIA's V100 GPU. But Rao's contention is that Lake Crest achieves a much better yield of its available flops than that of the V100 GPU. We should point out here that Rao actually never mentioned NVIDIA or the V100 explicitly, referring to the competing platform as "Chip X."

During his keynote, he threw up a chart comparing utilization rates that illustrated the semi-fictional Chip X could only deliver 27 teraflops on General Matrix-Matrix Multiplication (GEMM), a key operation common to many deep learning algorithms. On this same benchmark, Lake Crest was able to achieve 38 teraflops, which represents a 96 percent yield of available flops. Rao also noted that Lake Crest achieves nearly the same GEMM yield on two connected chips versus a single NPP. Whether that scales up to even larger number of processors – say eight or more – remains to be seen.

Of course, machine learning codes encompass a lot more than GEMM operations, so utilization rates are going to vary from application to application. (And we're sure NVIDIA will have something to say about this.) But it's certainly plausible that a custom-built machine learning chip would be more efficient at these types of codes than a more general-purpose processor like a GPU.

Lake Crest draws less than 210 watts, which compares to 300 watts for an NVLink V100 and 250 watts for the PCIe version. That will make these chips marginally easier to squeeze into datacenter servers than their more power-demanding GPU competition.

But apparently Lake Crest will never get the chance. The product won't be generally available since Intel only intends to release it in limited quantities as a "Software Development Vehicle." Rao says the first broadly available NNP processor will be Spring Crest, whose product designation is NNP-L1000. It's scheduled for general release in late 2019 and is anticipated to be three to four times faster than Lake Crest. That should put it in the range of 120 to 160 peak teraflops per chip.

Spring Crest will also include support for bfloat16, a numerical format that essentially squeezes a standard 32-bit floating value into a 16-bit float customized for tensor operations. It uses the same 8 bits for the exponent as a standard 32-bit float but allocates only 7 bits for the mantissa, which the AI gods have deemed to be enough for deep learning computation. The more compact format means bandwidth can be effectively doubled as data is shuttled around the system. It also enables chip architects to design smaller multiply units, which means more of them will fit onto a die.

Intel, Google, and perhaps others, are hoping bfloat16 becomes a standard numerical format for processing neural network. Over time, Intel plans to support this format across all their AI products, including the Xeon and FPGA lines.

Rao wrapped up the hardware roadmap portion of his presentation by revealing that Intel is working on a discrete accelerator for inferencing, the idea being to achieve the best possible performance per watt for. The AI chief wasn't able to share any details of the future chip, not even its code name. "Look for announcements coming up soon," he said.

0 👍

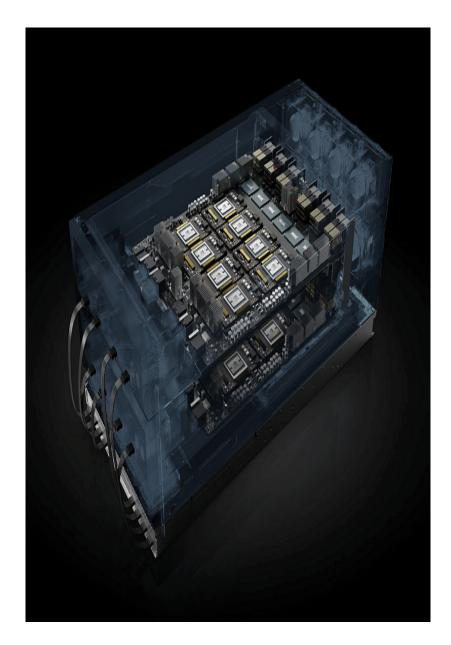

D 05/29/18--23:13: <u>NVIDIA Brings</u> <u>HPC and AI Under Single Platform</u> <u>with HGX-2</u> At Taiwan's GPU Technology Conference this week, NVIDIA founder and CEO Jensen Huang announced the HGX-2, a 16-GPU reference design aimed at some of the most computationally demanding HPC and AI workloads. As a reflection of its tightly integrated design, Jensen characterized the platform as the "the world's largest GPU."

HGX-2. Source NVIDIA

According to him, such an architecture can deliver significant priceperformance advantages for both high performance computing and machine learning environments compared to conventional CPU-based servers. The V100 processor, upon which the HGX-2 is based, offers both specialized Tensor Cores for deep learning acceleration, as well as more conventional IEEE floating point hardware to speed more traditional high performance

computing applications like physics simulations and weather modeling. "NVIDIA's HGX-2 with Tensor Core GPUs gives the industry a powerful, versatile computing platform that fuses HPC and AI to solve the world's grand challenges," Jensen declared. The HGX-2 is actually the design behind NVIDIA's own DGX-2 server product, which the company <u>launched in March at</u> <u>GTC in California</u>. That product was aimed primarily at machine learning users who wanted to be first in line to use the latest 32GB V100 GPUs in a tightly connected 16-GPU configuration.

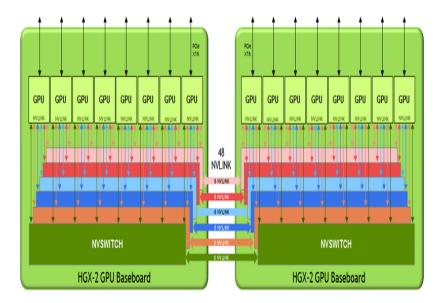

Connectivity is the key word here. The DGX-2, and now the HGX-2 upon which it is based, is comprised of 12 NVLink switches (NVSwitches), which are used to fully connect the 16 GPUs. Although that sounds simple enough, the design is a bit more involved. Briefly, the platform is broken up into two eight-GPU baseboards, each outfitted with six 18-port NVSwitches. Communication between the baseboards is enabled by a 48-NVLink interface. The switch-centric design enables all the GPUs to converse with one another at a speed of 300 GB/second -- about 10 times faster than what would be possible with PCI-Express. And fast enough to make the distributed memory act as a coherent resource, given the appropriate system software.

HGX-2 architecture. Source: NVIDIA

Not only does the high-speed communication makes it possible for the 16 GPUs to treat each other's memory as its own, it also enables them to behave as one large aggregated GPU resource. Since each of the individual GPUs has 32 GB of local high bandwidth memory, that means an application can access 512 GB at a time. And because these are V100 devices, that same application can tap into two petaflops of deep learning (tensor) performance or, for HPC, 125 teraflops of double precision or 250 teraflops of single precision. A handful of extra teraflops are also available from the PCIe-linked CPUs, in either a single-node or dual-node configuration (two or four CPUs, respectively).

That level of performance and memory capacity is enough to run some of the largest deep learning models and GPU-accelerated HPC simulations, without the need for a multi-server set-up. The HGX-2 can also be clustered into larger systems via 100Gbps network inferface cards, but at the expense of being force into a distributed computing model.

Of course, NVIDIA could just have just sold its own DGX-2 to serve these HPC and AI customers. But the company is not really in the system business and is not set up to build and deliver these machines in the kind of quantity it envisions. Making the HGX-2 design available to OEMs and ODM means it can reach a much larger audience, and theoretically sell a lot more V100 GPUs, not to mention NVSwitches.

In particular, making the platform available as a reference design will enable the HGX-2 to be deployed in cloud and other large-scale datacenter environments at volumes and price points that would have been impossible with the \$399,000 DGX-2. Lenovo, QCT, Supermicro and Wiwynn have announced plans deliver HGX-2-based servers later this year. In addition, ODMs Foxconn, Inventec, Quanta and Wistron revealed they are designing HGX-2 systems for "some of the world's largest cloud datacenters." Those systems are also expected to be available later in 2018.

Although NVIDIA is positioning the HGX-2 as a dual-use platform for HPC and Al, it's likely that most of the deployments, especially the ones that end up in cloud datacenters, will be primarily running deep learning workloads. That was certainly the case for HGX-1-based installations at Amazon, Facebook and Microsoft. At this point, only a small percentage of HPC work is currently being performed in the cloud and only a fraction of those applications are GPU-enabled.

On the other hand, if Lenovo, Supermicro or one or more of the other system providers manage to sell an HGX-2-based machine to an HPC customer, there is certainly the possibility that it will be used for both traditional simulation work and machine learning. As we've reported before, the use of such mixed workflows appears to be on the rise at nearly all large HPC installations and that trend is expected to continue. The major limiting factor here is that not all HPC applications are GPU-ready, but the presence of a super-sized virtual GPU in the HGX-2 makes that limitation easier to overcome.

Looking more broadly, HGX-2 appears to be part of a larger strategy at NVIDIA to provide acceleration technology that is flexible enough to serve both HPC and AI. In that sense, the HGX-2 is really just a server-level extension of the V100 itself. While there is something of <u>a gold rush to develop custom-built</u> <u>AI chips and servers</u>, the supercomputing world would seem to be best served by a unified solution.

Intel briefly flirted with such a product last year, with its AI-tweaked Knights Mill Xeon Phi processor, but the chipmaker has since <u>reversed course</u>. For a time, AMD seemed intent on bringing its CPU-GPU accelerated processing unit (APU) to the datacenter with the Opteron X series, but that product line appears to be stalled. The <u>recently unveiled Prodigy processor</u> from startup Tachyum could theoretically give NVIDIA a run for its money, but even if the technology lives up to its claims, bringing that chip to market and building a software ecosystem around it is going to take many years.

For the time being, that leaves the GPU-maker essentially unchallenged in the unified accelerator space. And that means HPC sites looking to support traditional supercomputing, with a little machine learning on the side, will have a pretty clear idea of which chips they'll be buying. Which is probably just the way NVIDIA likes it.

#### D6/06/18--01:51: <u>As Moore's Law</u> <u>Winds Down, Chipmakers Consider</u> <u>the Path Forward</u>

At this month's ISC High Performance conference, representatives from Intel, NVIDIA, Xilinx, and NEC will speak about the challenges they face as applications like machine learning and analytics are demanding greater performance at a time when CMOS technology is approaching its physical limits.

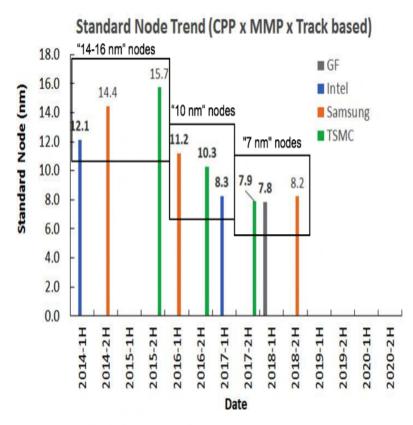

The four vendors will make their presentations during a 90-minute focus session called <u>Pushing Digital Computing to the Limits</u>, in which each representative will outline their company's strategy to advance their processor platforms over the next 12 years. During this period, Moore's Law, the observation that transistor size and density doubles every couple of years, will slowly come grinding to a halt.

The session will be led by Andreas Stiller, a veteran tech journalist who has covered processor hardware and technology for more than 30 years. Now mostly retired, Stiller continues to work as a freelancer and chairs conference sessions when the opportunities arise. We recently spoke with him to get his thoughts on where the chip industry is headed, especially as it relates to high performance computing, and what it means for the industry.

When talking with Stiller, one thing that becomes apparent is that he seems more optimistic about the longevity of silicon-based semiconductor technology than your average industry watcher. "I really see classical CMOS silicon for the next 20 or 25 years," he says. Stiller thinks the underlying technology will still be practical until we reach transistor geometries in the 1.5nm range.

Beyond that, he says, the silicon-based lattice structures simply won't support electron flow. Chipmakers could perhaps squeeze another half nanometer or so with more exotic materials like molybdenum compounds and carbon nanotubes, but in short order, they will bump up against their own physical limits.

That's the good news. The bad news is that we won't get to enjoy such 1.5nm transistors until around 2030. That's because the increasing difficulty of shrinking transistors is slowing the rate of Moore's Law. Thus, instead of going from 10nm to 7nm in one jump, chipmakers like Intel are looking to develop multiple iterations of the same node (i.e., 10nm, 10nm+, 10nm++) over the same timefram, with each version incorporating additional refinements, but with more or less the same transistor geometry.

That has real ramifications for the industry. For example, the delay of Intel's 10nm technology, which was originally scheduled for 2015/2016, has now been pushed all the way into 2019 for volume production. That delay probably had a role in <u>dooming the "Knights Hill" Xeon Phi processor and likely the entire product line</u>. The abandonment of Knights Hill resulted in the cancellation of the Department of Energy's original Aurora supercomputer, which will reappear in exascale form in 2021 with yet-to-be-determined processors.

When chipmakers can no longer count on better price-performance and performance-per-watt every two years by shrinking transistors, they need to do something else. In general, that something else means relying a lot more on design improvements. Of course, such improvements were always integral to processor design, but without the additional performance of moving to the next process node, architectural innovation becomes much more critical.

One indication that Moore's Law, and to an even greater degree, Dennard scaling, are no longer driving processor advances, is the growing importance of alternative chip architectures like GPUs and FPGAs. The fact that vendors like NVIDIA and Xilinx literally have a place at the table in Stiller's session alongside traditional chipmakers like Intel and NEC, is a reflection of the breakdown of these fundamental trends.

Stiller has become particularly interested in a new FPGA design Xilinx recently announced, which they call their adaptive compute acceleration platform (ACAP), which is a completely heterogeneous design that employs an FPGA fabric linking distributed memory, programmable DSP blocks, a multicore SoC, and one or more programmable compute engines, all connected via an on-chip network. Xilinx is promising performance and performance-per-watt that is

"unmatched by CPUs or GPUs." Xilinx CTO Ivo Bolsens plans to elaborate on the ACAP technology during his talk at the ISC session.

NVIDIA has perhaps benefited most from the declining fortunes of transistor shrinkage. The highly parallel architecture of the GPU has turned out to be a particularly good match for applications like machine learning and other types of advanced analytics. Since such a design is inherently less reliance on fast transistors, the company has carved out a sweet spot for itself, especially in the HPC and AI markets. Steve Oberlin, former Cray engineer and now CTO for NVIDIA's Tesla business, will speak about his company's plans to evolve their GPUs into the next decade. Maybe he'll even offer some hints about the company's post-Volta architecture.

Meanwhile NEC is looking to make a comeback with its latest vector processor, the SX-Aurora TSUBASA. Once thought too specialized, NEC is hoping the vector platform will get new life in a post-Moore's Law world. Given the inherent performance advantages of this architecture for HPC codes, vector chips may indeed become more attractive as semiconductor advances become less of a factor. Rudolf Fischer, who heads up the HPC technology group in Europe, will make the case for the future of vector processors.

Given Intel's current dominance of the HPC market with its Xeon processors, the company is the elephant in any room where processor technology is the topic. During the session, Al Gara, who was the chief architect at IBM in charge of the Blue Gene platform and now occupies a similar position in Intel's Data Center Group, will speak to the future technologies the chipmaker will bring to bear on the HPC market. Stiller is hoping (as are we) that Gara will elaborate on how the company plans to heal the Xeon/Xeon Phi divide as it moves its datacenter silicon into the exascale era.

Unfortunately, no one from OpenPower or ARM will be present to represent those two architectures. The 90-minute time allotment for Stiller's session isn't long enough to encompass the current level of chip diversity in the HPC chip space.

In addition, there will be no advocates for more exotic platforms like quantum, neuromorphic, and optical processors, all of which offer compelling alternatives for HPC work. Stiller expects each of these will come into play over the next 10 to 15 years, and of these, he thinks quantum computing offers the most exciting prospects. That said, he believes none of them will replace conventional digital processors any time soon. "For the foreseeable future,"he says, "we'll still have CPUs and GPUs."

For those attending ISC High Performance in Frankfurt Germany this month, this session will take place on Tuesday, June 26, from 8:30am to 10:00am, in the Panorama 2 room of Frankfurt Messe.

06/08/18--17:21: Summit Up and Running at Oak Ridge, Claims First Exascale Application

The Department of Energy's 200-petaflop Summit supercomputer is now in operation at Oak Ridge National Laboratory (ORNL). The new system is being touted as "the most powerful and smartest machine in the world."

And unless the Chinese pull off some sort of surprise this month, the new system will vault the US back into first place on the TOP500 list when the new rankings are announced in a couple of weeks. Although the DOE has not revealed Summit's Linpack result as of yet, the system's 200-plus-petaflop peak number will surely be enough to outrun the 93-petaflop Linpack mark of the current TOP500 champ, China's Sunway TaihuLight.

Even though the general specifications for Summit have been known for some time, it's worth recapping them here: The IBM-built system is comprised of 4,608 nodes, each one housing two Power9 CPUs and six NVIDIA Tesla V100 GPUs. The nodes are hooked together with a Mellanox dual-rail EDR InfiniBand network, delivering 200 Gbps to each server.

Assuming all those nodes are fully equipped, the GPUs alone will provide 215 peak petaflops at double precision. Also, since each V100 also delivers 125 teraflops of mixed precision, Tensor Core operations, the system's peak rating for deep learning performance is something on the order of 3.3 exaflops.

Those exaflops are not just theoretical either. According to ORNL director Thomas Zacharia, even before the machine was fully built, researchers had run a comparative genomics code at 1.88 exaflops using the Tensor Core capability of the GPUs. The application was rummaging through genomes looking for patterns indicative of certain conditions. "This is the first time anyone has broken the exascale barrier," noted Zacharia.

Of course, Summit will also support the standard array of science codes the DOE is most interested in, especially those having to do with things like fusion energy, alternative energy sources, material science, climate studies, computational chemistry, and cosmology. But since this is open science system available to all sorts of research that frankly has nothing to do with energy, Summit will also be used for healthcare applications in areas such as drug discovery, cancer studies, addiction, and research into other types of diseases. In fact, at the press conference announcing the system's launch, Zacharia expressed his desire for Oak Ridge to be "the CERN for healthcare data analytics."

The analytics aspect dovetails nicely with Summit's deep learning propensities, inasmuch as the former is really just a superset of the latter. When the DOE first contracted for the system back in 2014, the agency

probably only had a rough idea of what they would be getting Al-wise. Although IBM had been touting its data-centric approach to supercomputing prior to pitching its Power9-GPU platform to the DOE, the Al/machine learning application space was in its early stages. Because NVIDIA made the decision to integrate the specialized Tensor Cores into the V100, Summit ended up being an Al behemoth, as well as a powerhouse HPC machine.

As a result, the system is likely to be engaged in a lot of cutting-edge AI research, in addition to its HPC duties. For the time being, Summit will only be open to select projects as it goes through its acceptance process. In 2019, the system will become more widely available, including its use in the Innovative and Novel Computational Impact on Theory and Experiment (INCITE) program.

At that point, Summit's predecessor, the Titan supercomputer, is likely to be decommissioned. Summit has about eight times the performance of Titan, with five times better energy efficiency. When Oak Ridge installed Titan in 2012, it was the most powerful system in the world and is still fastest supercomputer in the US (well, now the second-fastest). Titan has NVIDIA GPUs too, but these are K20X graphics processors and their machine learning capacity are limited to four single precision teraflops per device. Fortunately, all the GPU-enabled HPC codes developed for Titan should port over to Summit pretty easily and should be able to take advantage of the much greater computational horsepower of the V100.

For IBM,

Summit represents a great opportunity to showcase its Power9-GPU AC922 server to other potential HPC and enterprise customers. At this point, the company's principle success with its Power9 servers has been with systems sold to enterprise and cloud clients, but generally without GPU accelerators. IBM's only other big win for its Power9/GPU product is the identically configured Sierra supercomputer being installed at Lawrence Livermore National Lab. The company seems to think its biggest opportunity with its V100-equipped server is with enterprise customers looking to use GPUs for database acceleration or developing deep learning applications in-house.

Summit will also fulfill another important role – that of a development platform for exascale science applications. As the last petascale system at Oak Ridge,

the 200-petaflop machine will be a stepping stone for a bunch of HPC codes moving to exascale machinery over the next few years. And now with Summit up and running, that doesn't seem like such a far-off prospect. "After all, it's just 5X from where we are," laughed Zacharia.

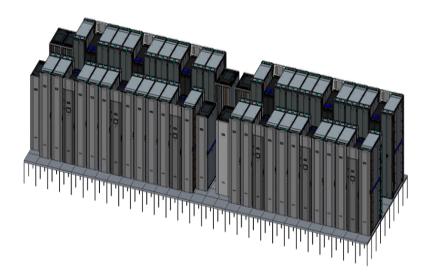

Top image: Summit supercomputer; Bottom image: Interior view of node. Credit: ORNL

#### D6/18/18--04:46: Sandia to Install <u>First Petascale Supercomputer</u> <u>Powered by ARM Processors</u>

Sandia National Laboratories will soon be taking delivery of the world's most powerful supercomputer using ARM processors. The system, known as Astra, is being built by Hewlett Packard Enterprise (HPE) and will deliver 2.3 petaflops of peak performance when it's installed later this year.

Astra rendering. Source: HPE

"Sandia National Laboratories has been an active partner in leveraging our Arm-based platform since its early design, and featuring it in the deployment of the world's largest Arm-based supercomputer, is a historical moment not just for us, but for the industry as we race toward achieving exascale computing," said Mike Vildibill, vice president, Advanced Technology Group, HPE

Astra will be based on HPE's Apollo 70 system and will be comprised of 2,592 dual-socket nodes, containing 145,000 cores – by far the largest such system

the company has delivered. If it was up and running today, it would easily make it into the upper fifth of the TOP500 list.

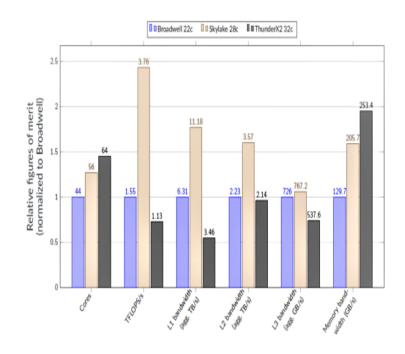

Each node will be equipped with two 28-core Cavium ThunderX2 processors running at 2.0 GHz. These aren't the biggest or the fastest of Cavium's newest ARM processor, but represents something of a sweet spot in priceperformance. In aggregate, the compute nodes will draw 1.2 MW of power, which translates into a respectable energy efficiency for a 2.3-petaflop machine.

Local storage will be supplied by Apollo A4520 enclosures, providing 350 TB in the form of an all-flash Lustre appliance. Because of the relatively small capacity and high performance, it will primarily be used for operations needing extreme I/O bandwidth – things like burst buffering and file checkpointing.

Prior to the Astra announcement, most of the other action with regard to ARMpowered HPC was taking place in the United Kingdom. HPE had previously announced that three UK universities (Edinburgh, Leicester, and Bristol) had ordered Apollo 70 clusters, but each of these systems will be outfitted with just 64 nodes and will top out at a mere 74 teraflops. As far as computational capacity goes, the closest thing to Astra is Isambard, <u>a 10,000-core Cray</u> <u>XC50 supercomputer using these same ThunderX2 processors</u>. It's set to be deployed at the Great Western 4 (GW4) Alliance, a research consortium of four UK universities (Bristol, Bath, Cardiff and Exeter).

Astra's delivery is the first production deployment of the of the Department of Energy's (DOE) National Nuclear Security Administration's (NNSA) Vanguard Project. The project's mission is to ensure a viable HPC ecosystem is established for ARM technology within the NNSA and the larger DOE community. Besides Sandia, a number of other national labs are involved in the project, including Lawrence Livermore, Oak Ridge, Argonne, and Los Alamos.

Over the next few years, these labs will help fill out the system software stack and perform application porting for various multi-physics codes, with the eventual goal of supporting ARM-based exascale systems at the agency. A number of ThunderX2-powered prototype clusters, based on pre-production Cavium silicon are already running at the labs, and are being used to develop operating system (OS) support, compilers, math libraries, file systems, and other elements of the toolchain. Lawrence Livermore, for example, has already ported the NNSA's Tri-Lab Operating System Stack (TOSS) to the ThunderX2 platform.

Given the size of Astra, it will be the first ARM system in the world that will be able to run HPC workloads at true supercomputing scale and demonstrate how much computational capacity can be extracted from the hardware. "One of the important questions Astra will help us answer is how well does the peak performance of this architecture translate into real performance for our mission applications," said Mark Anderson, program director for NNSA's Advanced Simulation and Computing program, which funds Astra.

Thanks to the local flash storage and the eight memory channels on each ThunderX2 socket, Astra is likely to be especially adept at analytics and other data-demanding codes. In particular, the eight-memory-design represents a 33 percent improvement on Intel's six-channel implementation of its Xeon Scalable processor. The better bandwidth is one of ThunderX2's most

important differentiating features and represents an attempt to provide a more balanced relationship between compute capacity and memory speed. (Note that you don't need an ARM processor to this; AMD has the same eight-memory-channel design with its x86 EPYC processor.)

This focus on optimizing data movement is due to the fact that this is where most of the system's energy is being consumed these days. "We can see clearly that the amount of power required to move data inside the system is an order of magnitude greater than the amount of power needed to compute that data," explained Vildibill.

That said, the DOE's main interest in ARM probably has more to do with the fact that it represents a third viable processor architecture for the datacenter and is poised to get much broader industry support. Maybe just as important though, the architecture is driven by an open licensing model than encourages innovation and diversity. And that model has already resulted in a partnership between ARM Ltd and Fujitsu to establish <u>an HPC implementation of ARM</u>, known as the ARMv8-A Scalable Vector Extension (SVE). It's set to debut in the Post-K supercomputer, Japan's initial exascale system that is scheduled to be installed at RIKEN in 2021-2022. Future features, such as on-package high bandwidth memory and integrated high-performance interconnects are already being anticipated.

Astra is scheduled for deployment in late summer. It will be installed at Sandia in a part of a datacenter that originally housed the Red Storm supercomputer.

####

On Wednesday evening at the ISC High Performance conference, HPC luminary Dr. Thomas Sterling will deliver his customary keynote address on the state of high performance computing. To get something of a preview of that talk, we caught up with Sterling and asked him about some of the more pressing topics in the space.

What follows is pretty much the unedited text or our email exchange.

### TOP500 News: What do you think the achievement of exascale computing will mean to the HPC user community?

**Thomas Sterling:** As a particular point in capacity and capability, exascale is as arbitrary in the continuum of performance as any other. But symbolically it is a milestone in the advancement of one of mankind's most important technologies, marking unprecedented promise in modeling and information management.

Of a subtler nature, it is a beachhead on the forefront of nanoscale enabling technologies, marking the end of Moore's Law, the flatlining of clock rates due to power considerations, and the limitations of clock rate. The achievement of

exascale computing will serve as an inflection point at which change from conventional means is not only inevitable but essential. It also implies the need to replace the venerable von Neumann architecture of which almost all commercial computing

systems of the last seven decades are derivatives thereof.

Many will correctly argue the specific metrics by which this point is measured but at any dimension, it reflects progress, even if not as much as the community would like to think. This last consideration is a reflection of the Olympian heights at which almost all computing is excluded. The reality is that almost all systems operate at about two orders of magnitude lower capability. But then, most of us do not drive a Rolls Royce, while still admiring it.

## TOP500 News: Do you think it's important which nation reaches that milestone first?

**Sterling:** It would be easy to dismiss the importance of the exact order in which nations realize exascale capability, in particular, based on High Performance Linpack (HPL). Perhaps a far more important metric is a nation's per capita number of systems deployed on the TOP500 list, suggesting the degree of access for high-end computing; this suggests that the number 500 system is the more important line on any such curve.

Further, thoughtful practitioners correctly observe that the accomplishment is the actual amount of science and engineering achieved as well as other important tasks, not an artificial test that has meaningful consequences. Finally, it's not even clear that we are looking at all of the world's big machines with industry deploying and operating enormous conglomerates of processing components and not even participating in the Linpack marathon.

Intellectually I agree with all of these cogent viewpoints. But there is an emotional aspect of this milestone and we are a species driven more by emotions than we are by predicate calculus. A nation is one delineation of a society and people – even HPC people – are atomic elements of societies. If a nation and therefore a societal identity is measured as competitive, then we as individuals inherit that property, sense of satisfaction – yes, even pride – and the tools of future achievement to which HPC contributes. If we fail significantly, then we accept our lesser stature. It does not so much matter who is at the front of the line around the race track at any instance. But it does matter if we are part of the race.

TOP500 News: Potential exascale achievements aside, how much do you worry about the ascendance of China in HPC?

**Sterling:** The recent dominance of China is important and of a concern, not that it is a Chinese accomplishment, but rather that it demonstrates a potential diminishing of US will, means, and ability of delivering the best that enabling technology can offer. I applaud the Chinese advances as well as those of Europe and Japan. The K machine has been at the top of the <u>Graph 500 list</u> and Europe is exploring alternative hardware structures for future HPC.

More, the Chinese have demonstrated significant innovation and are also competitive in terms of number of deployed HPC systems. They are learning a lot about how to apply these machines to real world applications rather than just paying for them. US funding has stalled and research in HPC has declined precipitously. Even with a recent increase in HPC budget by the US Senate, this has not been refactored into US HPC research but rather in system deployment. While <u>Summit</u> is a meaningful and long-awaited demonstration of American engagement in HPC progress, what does the <u>failure of the Aurora project</u> of similar scale portend for the future. It is not the Chinese success I worry about, it is the US stagnation I fear.

TOP500 News: What's your perspective on the impact of machine learning and the broader area of data analytics on supercomputing – from both its effect on how its driving hardware – processors, memory, networking, etc. – and on how HPC practitioners are incorporating machine learning into their traditional workflows?

**Sterling:** The techniques at the core of machine learning go back to the 1980's – neural-nets – and while creditable improvements have been inaugurated, the foundations are clearly similar. The important advance, even leap-frogging, is the explosive applications to unprecedented scale of data to which HPC is now being put to use. With little fear of contradiction, machine learning and data analytics is a major extension and market of HPC.

Further, it gives us a window into disorganized data sources in part made available through the internet and from many disparate origins from giant science experiments like the Large Hadron Collider, to existing and of criticality, for example, personalized medicine. I hope that these emerging data-intensive applications will stimulate innovative concepts in the memory side of supercomputer architecture with less focus on the FPU and more on the memory semantics, latency, bandwidth, and parallelism. It is long overdue.

But it should be noted that the term "machine learning" should not be misconstrued to mean machine intelligence. It is people who learn from the data processing of this paradigm, gaining human understanding and knowledge, not the machines. Machines do not know how to process the knowledge gained by human practitioners and they certainly don't achieve anything like "understanding". For this, we need yet new breakthroughs to reach Machine Intelligence (MI).

TOP500 News: There seem to be three computing technologies on the horizon that could potentially disrupt the market: quantum computing, neuromorphic computing, and optical computing. Can you give us your perspective on the potential of each of these for HPC kinds of applications?

**Sterling:** The three identified technologies are certainly part of the exploratory road map "on the horizon" as you say. But they are neither alone nor necessarily the top three. The enormous funding being poured into quantum computing by industry and government is very positive and will ultimately lead to a new form of computing far different from conventional practices, and as distinct as <u>Vannevar Bush</u> machines were from the succeeding von Neumann generation. Quantum computing will be important but always serving domain-specific purposes where their advantages can be exploited.

Neuromorphic or "brain-inspired" computing is intriguing as it is uncertain. The diversity of approaches being explored is constructive as ideas and insights emerge through a human relaxation process. I personally don't think it's going to work the way many people think. For example, I don't think we have to mimic the structural elements of the brain to achieve machine intelligence. But I do expect that the associative methods hardwired into the brain if duplicated in some analogous fashion will greatly enhance certain idioms of processing that are very slow with today's conventional methods. Right now, the inspiration is catalyzing new ideas and resulting methods that are worth exploring. Who knows what we will find.

Optical computing in the sense of adopting optical technologies to digital computing have been heavily pursued but in active data storage and logical data transformation have not proved successful. I love the idea but do not have faith in its promise. However, optical in the analogous sense employing non-linear functionality in the analog versus digital means may be very promising in the long term – or not. A form of extreme heterogeneity mixing the strengths of optical in narrow operations with parallel digital systems may serve in a manner similar to structures integrating GPUs today.

But I'll close here by mentioning two other possibilities that, while not widely considered currently, are nonetheless worthy of research. The first is superconducting supercomputing and the second is non-von Neumann architectures. Interestingly, the two at least in some forms can serve each other making both viable and highly competitive with respect to future post-exascale computing designs. Niobium Josephson Junction-based technologies cooled to four Kelvins can operate beyond 100 and 200 GHz and has slowly evolved over two or more decades. When once such cold temperatures were considered a show stopper, now quantum computing – or at least quantum annealing – typically is performed at 40 milli-Kelvins or lower, where four Kelvins would appear like a balmy day on the beach. But latencies measured in cycles grow proportionally with clock rate and superconducting supercomputing must take a very distinct form from typical von Neumann cores; this is a controversial view, by the way.

Possible alternative non-von Neumann architectures that would address this challenge are cellular automata and data flow, both with their own problems, of course – nothing is easy. I introduce this thought not to necessarily advocate for a pet project – it is a pet project of mine – but to suggest that the view of the future possibilities as we enter the post-exascale era is a wide and exciting field at a time where we may cross a singularity before relaxing once again on a path of incremental optimizations.

I <u>once said</u> in public and in writing that I predicted we would never get to zettaflops computing. Here, I retract this prediction and contribute a contradicting assertion: zettaflops can be achieved in less than 10 years if we

adopt innovations in non-von Neumann architecture. With a change to cryogenic technologies, we can reach yottaflops by 2030.

Thomas Sterling's ISC <u>keynote address</u> will take place at the Messe Frankfurt on Wednesday, June 27, at 5:30 - 6:15 pm CEST.

# 06/24/18--17:37: <u>US Regains</u> <u>TOP500 Crown with Summit</u> <u>Supercomputer, Sierra Grabs Number Three Spot</u>

FRANKFURT, Germany; BERKELEY, Calif.; and KNOXVILLE, Tenn.-The

TOP500 celebrates its 25<sup>th</sup> anniversary with a major shakeup at the top of the list. For the first time since November 2012, the US claims the most powerful supercomputer in the world, leading a significant turnover in which four of the five top systems were either new or substantially upgraded.

Summit supercomputer. Source: Oak Ridge National Laboratory

Summit, an IBM-built supercomputer now running at the Department of Energy's (DOE) Oak Ridge National Laboratory (ORNL), captured the number

one spot with a performance of 122.3 petaflops on High Performance Linpack (HPL), the benchmark used to rank the TOP500 list. Summit has 4,356 nodes, each one equipped with two 22-core Power9 CPUs, and six NVIDIA Tesla V100 GPUs. The nodes are linked together with a Mellanox dual-rail EDR InfiniBand network.

Sunway TaihuLight, a system developed by China's National Research Center of Parallel Computer Engineering & Technology (NRCPC) and installed at the National Supercomputing Center in Wuxi, drops to number two after leading the list for the past two years. Its HPL mark of 93 petaflops has remained unchanged since it came online in June 2016.

Sierra, a new system at the DOE's Lawrence Livermore National Laboratory took the number three spot, delivering 71.6 petaflops on HPL. Built by IBM, Sierra's architecture is quite similar to that of Summit, with each of its 4,320 nodes powered by two Power9 CPUs plus four NVIDIA Tesla V100 GPUs and using the same Mellanox EDR InfiniBand as the system interconnect.

Tianhe-2A, also known as Milky Way-2A, moved down two notches into the number four spot, despite receiving a major upgrade that replaced its fiveyear-old Xeon Phi accelerators with custom-built Matrix-2000 coprocessors. The new hardware increased the system's HPL performance from 33.9 petaflops to 61.4 petaflops, while bumping up its power consumption by less than four percent. Tianhe-2A was developed by China's National University of Defense Technology (NUDT) and is installed at the National Supercomputer Center in Guangzhou, China.

The new AI Bridging Cloud Infrastructure (ABCI) is the fifth-ranked system on the list, with an HPL mark of 19.9 petaflops. The Fujitsu-built supercomputer is powered by 20-core Xeon Gold processors along with NVIDIA Tesla V100 GPUs. It's installed in Japan at the National Institute of Advanced Industrial Science and Technology (AIST).

Piz Daint (19.6 petaflops), Titan (17.6 petaflops), Sequoia (17.2 petaflops), Trinity (14.1 petaflops), and Cori (14.0 petaflops) move down to the number six through 10 spots, respectively.

#### **General highlights**

Despite the ascendance of the US at the top of the rankings, the country now claims only 124 systems on the list, a new low. Just six months ago, the US had 145 systems. Meanwhile, China improved its representation to 206 total systems, compared to 202 on the last list. However, thanks mainly to Summit and Sierra, the US did manage to take the lead back from China in the performance category. Systems installed in the US now contribute 38.2 percent of the aggregate installed performance, with China in second place with 29.1 percent. These numbers are a reversal compared to six months ago.

The next most prominent countries are Japan, with 36 systems, the United Kingdom, with 22 systems, Germany with 21 systems, and France, with 18 systems. These numbers are nearly the same as they were on the previous list.

For the first time, total performance of all 500 systems exceeds one exaflop, 1.22 exaflops to be exact. That's up from 845 petaflops in the November 2017

list. As impressive as that sounds, the increase in installed performance is well below the previous long-term trend we had seen until 2013.

The overall increase in installed capacity is also reflected in the fact that there are now 273 systems with HPL performance greater than one petaflop, up from 181 systems on the previous list. The entry level to the list is now 716 teraflops, an increase of 168 teraflops.

#### **Technology trends**

Accelerators are used in 110 TOP500 systems, a slight increase from the 101 accelerated systems in the November 2017 lists. NVIDIA GPUs are present in 96 of these systems, including five of the top 10: Summit, Sierra, ABCI, Piz Daint, and Titan. Seven systems are equipped with Xeon Phi coprocessors, while PEZY accelerators are used in four systems. An additional 20 systems now use Xeon Phi as the main processing unit.

Almost all the supercomputers on the list (97.8 percent) are powered by main processors with eight or more cores and more than half (53.2 percent) have over 16 cores.